# Biological Development model for the Design of Robust Digital System

**Heng Liu**

**Doctor of Philosophy**

**Intelligent Systems Research Group**

**Electronics Department**

**University of York**

September 2007

## **Abstract**

This thesis presents a biologically-inspired developmental model for the design of digital circuits. Circuits have been evolved that exhibit the ability to self-repair and correct transient faults to recover correct functionality. The method devised gives no explicit coordinate information to the evolved cell circuits.

The method presented has been implemented fully in electronic hardware. This allowed developmental circuits to be evolved considerably more quickly than in software simulation.

The methods presented have been applied to produce a self-repairing two bit multiplier and an autonomous robot controller circuit. Results are presented that shows that after introduction of faults, both circuits can autonomously recover correct functionality.

## **Keywords**

Fault-tolerance, Evolvable hardware, FPGA, Development principle, Multicellular organism, Evolutionary algorithm, Cartesian Genetic Programming, French Flag, Multiplier, Digital circuit, Autonomous Robot Controller

# **Acknowledgement**

No matter how much to write, it is just impossible to express my deep and genuine appreciation to every person who supported and contributed to my research in terms of financial, technical and mental aspects. I will try my best to acknowledge those without whom it would have been less productive or even impossible.

Without the unconditional financial support from my parents, the study of my Britain degree would have been absolutely unfeasible at all. Furthermore, they have always had intuitive ideas, constructive suggestions and supportive encouragement; especially during I am in the most arduous situation of my research. I am proud of being born in this family and being your son.

This research was made possible under the excellent supervision of Prof. Andy Tyrrell and Dr. Julian Miller. I would like to thank them for their continuous support and guidance of the project as well as their suggestions and direction. In addition, I highly appreciate the efforts they exerted to find financial support for my further research.

To my wife, Mrs. Fei Xu, who is ready to give me unconditional backup and encourage me whenever I encounter problems. You know, it is hard for both of us in the year I am abroad. However we together make it! We love each other no less than, if not more than, one year ago. I am proud of being your companions. Thank you for all your valuable support and the peace of mind feeling you grant me.

My lab mates, Andy, Marcus, Dapeng Xu, Chao Wu, Rachael and Simon, also deserve my credit. Thanks for all your assistance and suggestions, as well as the laughs and times shared with me.

To my dear friends with whom I have had plenty of un-forgettable wonderful time, it has been a real fortune having you such good friends to communicate with, express my feelings and discuss general topics.

| Abstract                             | i                |

|--------------------------------------|------------------|

| Keywords                             | i                |

| Acknowledgement                      | ii               |

| Figure Index                         | ix               |

| Table Index                          | xii              |

| Chapter 1 Introduction               | 1                |

| 1.1 Research Motivation and Obje     | ective3          |

| 1.2 Hypothesis                       | 4                |

| 1.3 Achievements                     | 4                |

| 1.4 Structure of the Thesis          | 5                |

| Chapter 2 Evolutionary Design of Ele | ctronic Systems7 |

| 2.1 Introduction                     | 7                |

| 2.2 Principles of Evolutionary De    | sign9            |

| 2.3 Evolutionary Algorithms          | 13               |

| 2.3.1 Common Features                | 13               |

| 2.3.2 Overview of EAs                | 16               |

| 2.3.3 Comparison of different EA     | s18              |

| 2.4 Evolvable Hardware               | 19               |

| 2.4.1 Classification of Evolvable    | Hardware19       |

| 2.4.2 Extrinsic Evolvable Hardwo     | are20            |

| 2.4.3 Intrinsic Evolvable Hardwo     | ıre22            |

| 2.5 Limitation of EHW                | 24               |

| 2.6 Sum      | nmary                                           | 24 |

|--------------|-------------------------------------------------|----|

| Chapter 3 De | evelopment Principles and Development Systems   | 26 |

| 3.1 Biol     | logical Development Principles                  | 26 |

| 3.1.1 B      | Casic Concepts                                  | 26 |

| 3.1.1.1      | Chromosomes and Genes                           | 27 |

| 3.1.1.2      | 2 Genotype and Phenotype                        | 27 |

| 3.1.2 B      | Piological Living Organism Cells                | 28 |

| 3.1.3 St     | tages of Development                            | 30 |

| 3.1.4 C      | Characteristics of Biological Development       | 31 |

| 3.2 Mat      | thematical Abstractions of Development          | 32 |

| 3.2.1 G      | Gene Regulatory Network Abstractions            | 32 |

| 3.2.2 L      | -Systems                                        | 33 |

| 3.3 Dev      | velopmental Systems                             | 35 |

| 3.3.1 G      | Gene Regulatory Networks                        | 35 |

| 3.3.2 L      | -Systems and other Rewriting Rule Based Systems | 37 |

| 3.3.3 C      | Cell Programs                                   | 39 |

| 3.3.4 O      | Other Systems                                   | 40 |

| 3.4 Sum      | nmary                                           | 43 |

| Chapter 4 Fa | ult-tolerant Techniques                         | 44 |

| 4.1 Fun      | damental Concepts and Definitions               | 44 |

| 4.1.1 C      | Classification of System Faults                 | 46 |

| 4.1.2 P      | Phases of Fault Tolerance                       | 48 |

| 4.1.2.1      | l Error detection                               | 48 |

| 4.1.2.2      | 2 Damage confinement and assessment             | 49 |

| 4.1.2.3      | B Error recovery                                | 49 |

| 4124         | 4 Fault treatment and continued system service  | 50 |

| 4.2    | History of Fault Tolerance Systems                       | 50 |

|--------|----------------------------------------------------------|----|

| 4.3    | Conventional Fault-tolerant Design                       | 52 |

| 4.3    | 3.1 Hardware Redundancy                                  | 52 |

| 4.3    | 3.2 Information Redundancy                               | 53 |

| 4.3    | 3.3 Software Redundancy                                  | 54 |

| 4.3    | 3.4 Time Redundancy                                      | 54 |

| 4.4    | Conventional Transient Fault-tolerant Techniques         | 54 |

| 4.5    | Bio-inspired Fault-tolerant Techniques                   | 55 |

| 4.5    | 5.1 Phylogeny                                            | 56 |

| 4.5    | 5.2 Ontogeny                                             | 56 |

| 4.5    | 5.3 Epigenesis                                           | 57 |

| 4.6    | Summary                                                  | 57 |

| Chapte | er 5 Development Cellular Model for Digital System       | 59 |

| 5.1    | Transforming of Biological Principles to Digital Systems | 59 |

| 5.2    | Design Consideration                                     | 61 |

| 5.3    | Digital Cell Structure and Inter-Cell Connections        | 63 |

| 5.4    | Chemical Diffusion                                       | 67 |

| 5.5    | Digital Organism Growth                                  | 68 |

| 5.6    | Boundary Condition                                       | 70 |

| 5.7    | Cartesian GP and Genotype Representation                 | 70 |

| 5.8    | Summary                                                  | 72 |

| Chapte | er 6 Software Simulation of a Pattern Problem            | 73 |

| 6.1    | A Pattern Formation Problem: French Flag                 | 73 |

| 6.2    | Multi-Breed Evolution Algorithm                          | 74 |

| 6.3    | EO Evolutionary Computation Framework                    | 78 |

| 6.4    | Experiment                                               | 79 |

| 6.5       | Results                                          | 81  |

|-----------|--------------------------------------------------|-----|

| 6.6       | Analysis                                         | 82  |

| 6.6.1     | Comparison with previous research                | 83  |

| 6.6.2     | Robustness Analysis                              | 84  |

| 6.6.3     | Inputs and Molecules usages analysis             | 87  |

| 6.7       | Summary                                          | 89  |

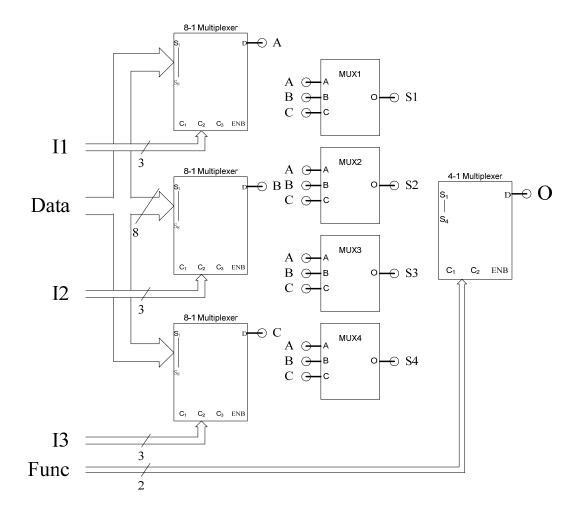

| Chapter ' | 7 Implementation of Digital Logic System         | 91  |

| 7.1       | Digital Organism Structure                       | 91  |

| 7.2       | Incorporating Execution Unit                     | 91  |

| 7.3       | Software Simulation                              | 93  |

| 7.3.1     | Evolution Strategy                               | 93  |

| 7.3.2     | Parameters                                       | 94  |

| 7.3.3     | Outcome of Simulation                            | 95  |

| 7.4       | Hardware Implementation of the Digital Organism  | 96  |

| 7.4.1     | Top Level Structure                              | 96  |

| 7.4.2     | Sub-Circuits Evolved via Software Evolution      | 97  |

| 7.5       | Hardware Simulation and Verification             | 97  |

| 7.6       | Summary                                          | 101 |

| Chapter 8 | 8 IEWH Implementation of 2-bit multiplier        | 103 |

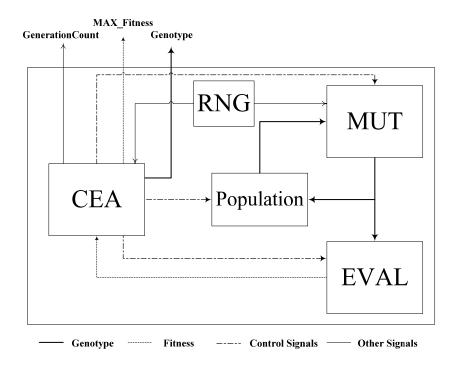

| 8.1       | Design of the Intrinsic Evolvable Hardware       | 103 |

| 8.1.1     | Evolvable Molecule: the Basic Element in the EHW | 104 |

| 8.1.2     | Evolutionary Algorithm                           | 105 |

| 8.1.3     | Overview of the EHW                              | 106 |

| 8.1.4     | Top-level Hardware Modules in the IEHW           | 106 |

| 8.1.5     | Execution Phase of the IEHW                      | 109 |

| 8.2       | Hardware Platform                                | 110 |

| 8.3    | Develop Environment                         | 110 |

|--------|---------------------------------------------|-----|

| 8.4    | Experiment and Results                      | 111 |

| 8.4    | 4.1 IEHW Parameters                         | 111 |

| 8.4    | 4.2 Synthesis Report                        | 112 |

| 8.4    | 4.3 Results of Experiment                   | 113 |

| 8.5    | Summary                                     | 113 |

| Chapte | er 9 Evolution of Sequential Digital System | 115 |

| 9.1    | Introduction                                | 115 |

| 9.2    | Adaptive Behaviour                          | 116 |

| 9.3    | Robust Random Access Memory                 | 118 |

| 9.3    | 3.1 1-Bit Primitive RAM Implementation      | 119 |

| Ģ      | 9.3.1.1 Input and Output Configuration      | 119 |

| Ģ      | 9.3.1.2 Experiments                         | 120 |

| 9.3    | 3.2 Towards Larger Robust RAM               | 121 |

| Ģ      | 9.3.2.1 Modification to the Model           | 121 |

| Ģ      | 9.3.2.2 Memory Unit Interface               | 122 |

| Ģ      | 9.3.2.3 Experiment Result                   | 122 |

| 9.4    | Discussion                                  | 123 |

| 9.5    | Summary                                     | 124 |

| Chapte | er 10 Autonomous Robot Controller           | 125 |

| 10.1   | Introduction                                | 125 |

| 10.    | .1.1 Robot and Application                  | 125 |

| 10.    | .1.2 Autonomous Robot Controller            | 126 |

| 10.2   | Robot and its Environment Setup             | 126 |

| 10.    | .2.1 Kiki Robot                             | 126 |

| 10     | 2.2 Robotic Task and Environment            | 127 |

| 10.3      | Webots Simulation                           | 128 |

|-----------|---------------------------------------------|-----|

| 10.3.     | 1 Introduction to Webots                    | 128 |

| 10.3.     | 2 Evolutionary Framework Deployed in Webots | 129 |

| 10        | 0.3.2.1 Robot Controller                    | 129 |

| 10        | 0.3.2.2 Supervisor Controller               | 129 |

| 10.3.     | 3 Experiments and Results                   | 130 |

| 10.4      | Discussion                                  | 133 |

| 10.5      | Summary                                     | 135 |

| Chapter 1 | 11 Conclusions                              | 137 |

| 11.1      | Summary and Achievement                     | 137 |

| 11.2      | Further Research Areas                      | 139 |

| Reference | e                                           | 141 |

| Appendix  | x                                           | 158 |

| Append    | dix A Schematics of Circuits for multiplier | 158 |

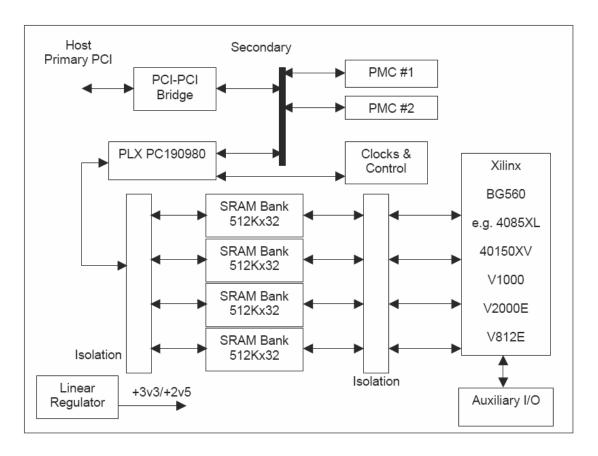

| Append    | dix B RC1000 Board from Celoxica            | 160 |

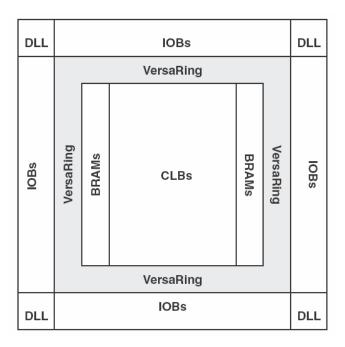

| Append    | dix C XCV1000 FPGA from Xilinx              | 162 |

| Append    | dix D World setup in Webot                  | 165 |

| Append    | dix E Introduction to EO                    | 166 |

# Figure Index

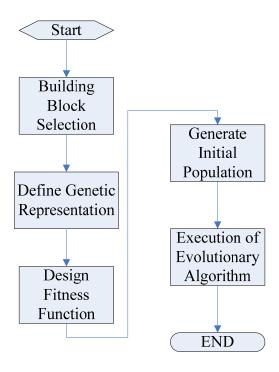

| Figure 2-1 Flow Chart of Evolutionary Design                                | 9      |

|-----------------------------------------------------------------------------|--------|

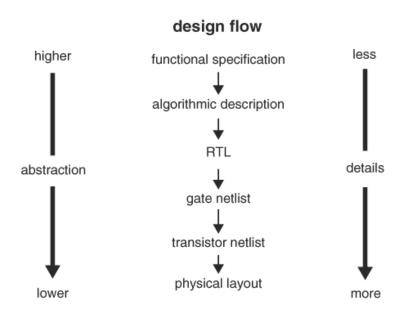

| Figure 2-2 Conventional Circuit Design Flow.                                | 10     |

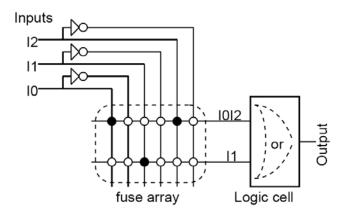

| Figure 2-3 Simplified PLD Structure                                         | 11     |

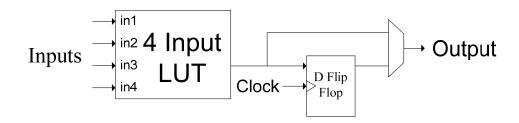

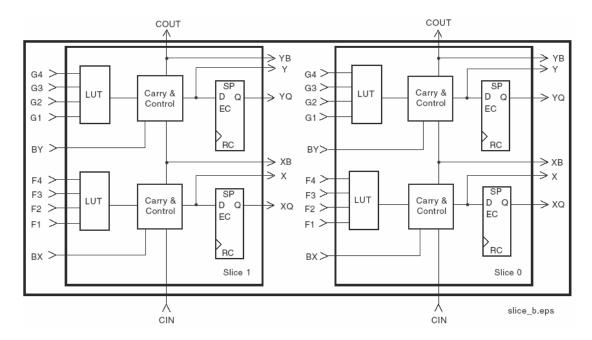

| Figure 2-4 Typical Configurable Logic Block Architecture                    | 12     |

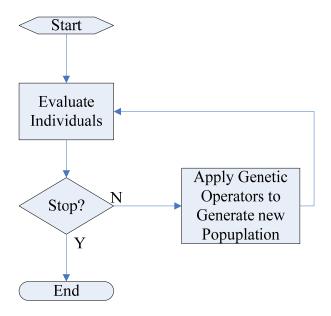

| Figure 2-5 Flow chart of common EA                                          | 14     |

| Figure 2-6 Mutation in Binary Encoding EA                                   | 15     |

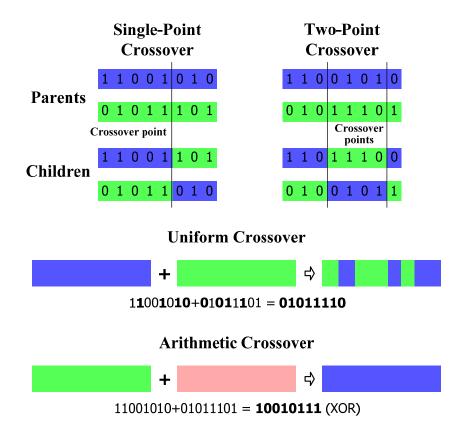

| Figure 2-7 Crossover in Binary Encoding EA                                  | 15     |

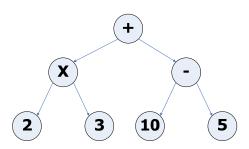

| Figure 2-8 GP Genotype Demonstration                                        | 17     |

| Figure 2-9 Circuit Representation in Miller's work                          | 21     |

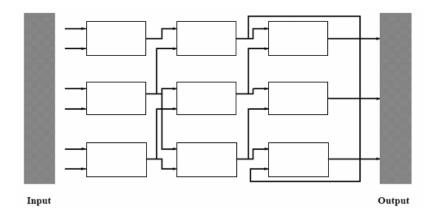

| Figure 2-10 Architecture of VRC [150]                                       | 22     |

| Figure 3-1 Overview Biological Cell Structure                               | 29     |

| Figure 3-2 Differentiation of tissues                                       | 31     |

| Figure 3-3 'Weeds' generated from a L-system in three dimensions [109]      | 34     |

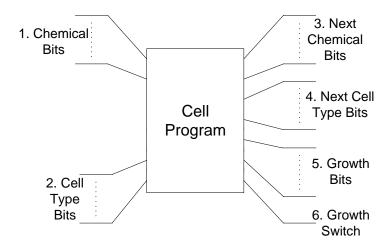

| Figure 3-4 Illustration of Cell Program Structure in Development CGP        | 40     |

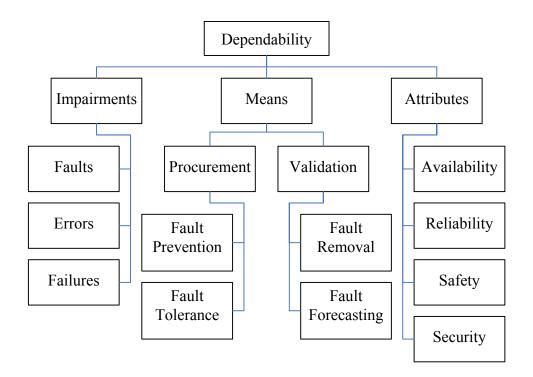

| Figure 4-1 Computer system dependability tree designed by Baron et al. [15] | 52].45 |

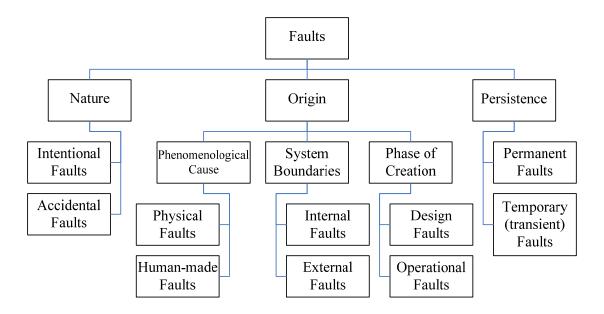

| Figure 4-2 Faults classification Categories [152]                           | 46     |

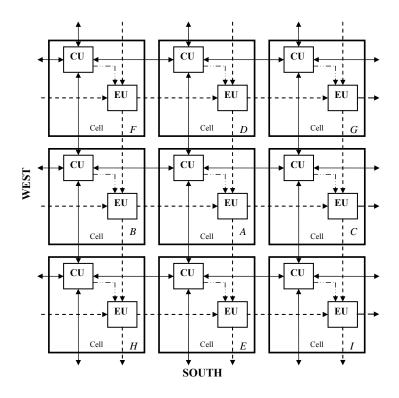

| Figure 5-1 Digital Organism Structure                                       | 63     |

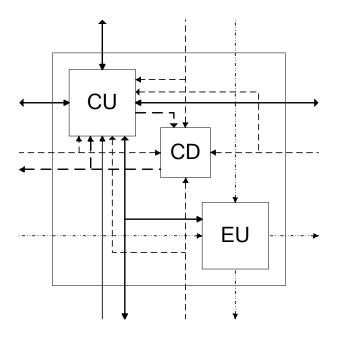

| Figure 5-2 Digital Cell Structure                                           | 64     |

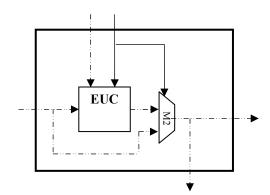

| Figure 5-3 Control Unit Structure                                           | 65     |

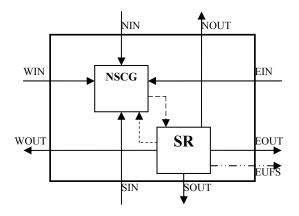

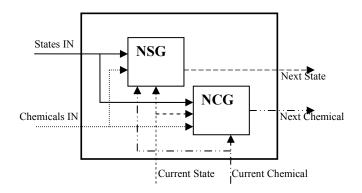

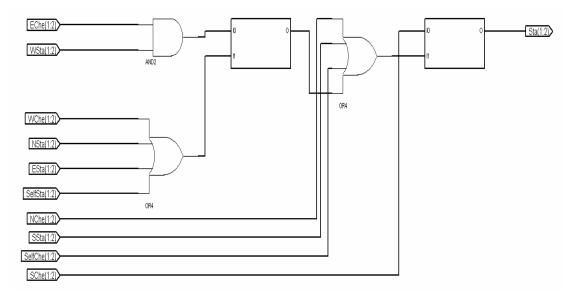

| Figure 5-4 NSCG Structure                                                   | 66     |

| Figure 5-5 Execution Unit Structure                                         | 66     |

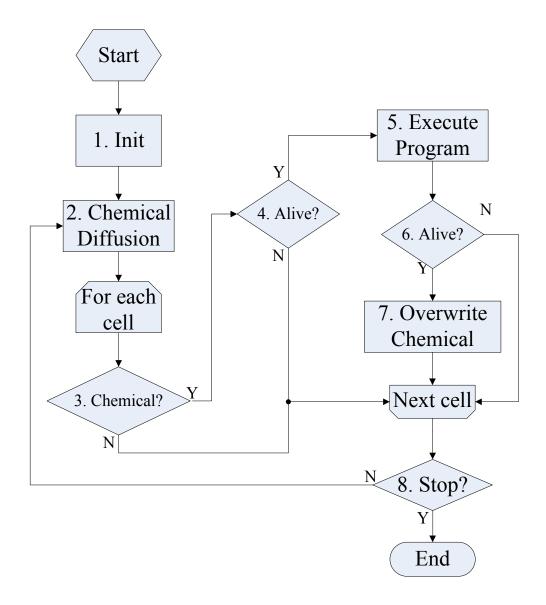

| Figure 5-6 Flow chart of the digital organism growth procedure              | 69     |

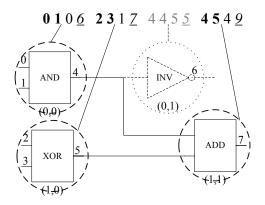

| Figure 5-7 A sample digital circuit                                         | 71     |

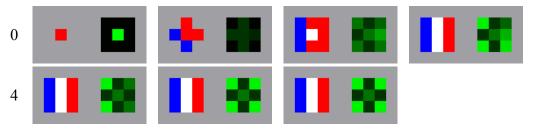

| Figure 6-1 Perfect Cell State Pattern for French Flag problem               | 74     |

# Figure Index

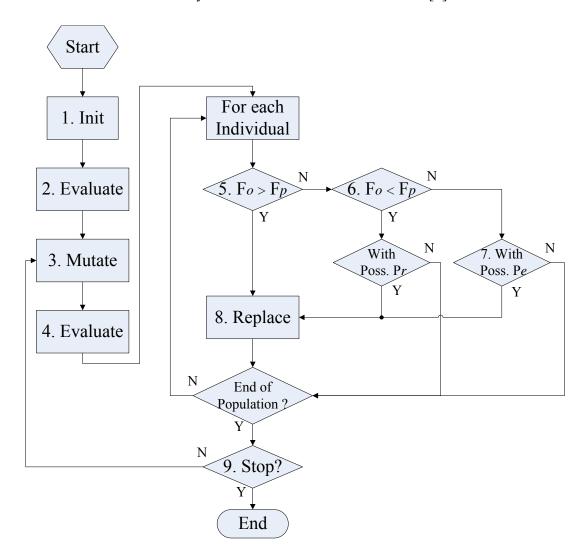

| Figure 6-2 Flow Diagram of the Evolution Algorithm Proposed                            | / 5   |

|----------------------------------------------------------------------------------------|-------|

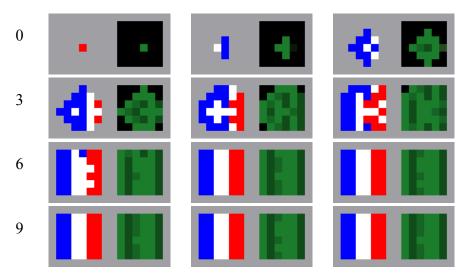

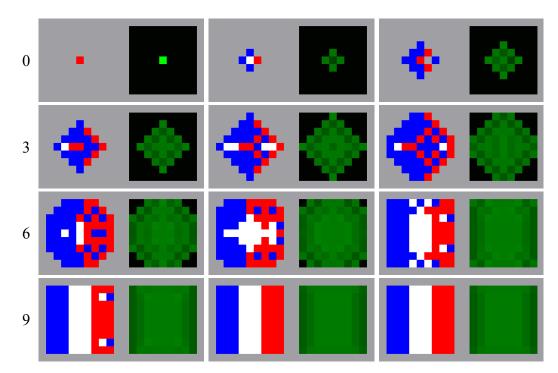

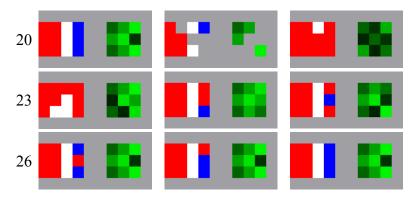

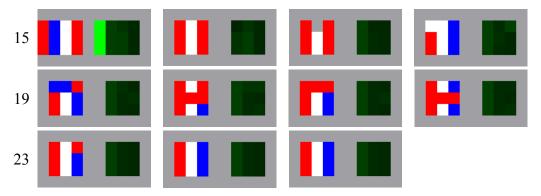

| Figure 6-3 Growth of one of the best 6x6 individuals                                   | 81    |

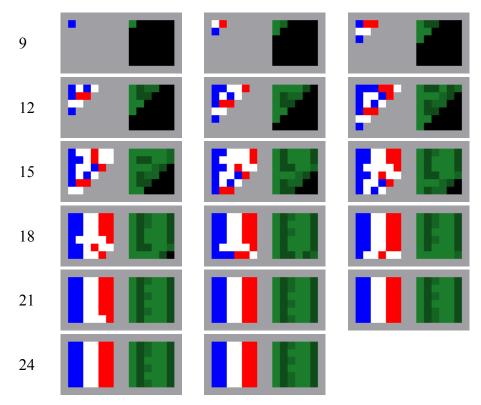

| Figure 6-4 Recovery Process of the 6x6 robust individual                               | 82    |

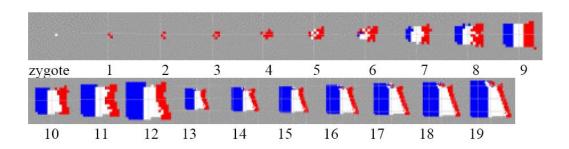

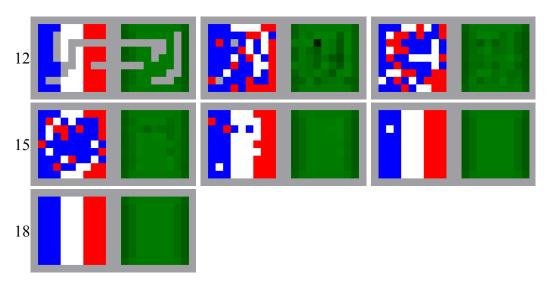

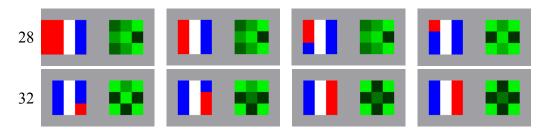

| Figure 6-5 Best solution for FF formation                                              | 83    |

| Figure 6-6 Recovery of the best FF solution                                            | 84    |

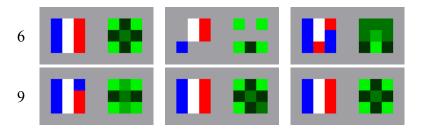

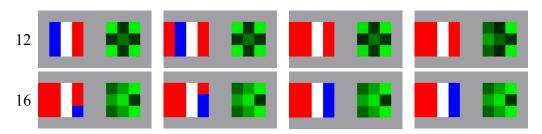

| Figure 6-7 Growth of one of the robust 9x9 individuals                                 | 85    |

| Figure 6-8 Recovery process from a random erasing of states/chemicals o 9x9 individual |       |

| Figure 6-9 Recovery from a single cell of the 9x9 French flag                          | 86    |

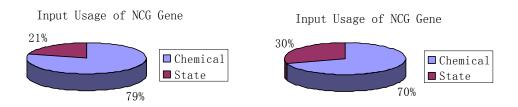

| Figure 6-10 Input usage of the two Genes encoding a French flag                        | 88    |

| Figure 6-11 Chemical signal usage details                                              | 88    |

| Figure 6-12 Normalized molecule usage in the best solutions                            | 89    |

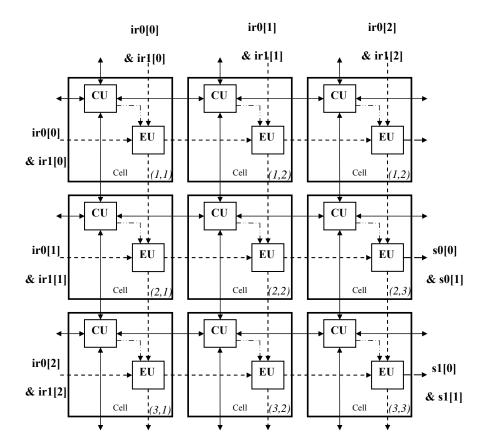

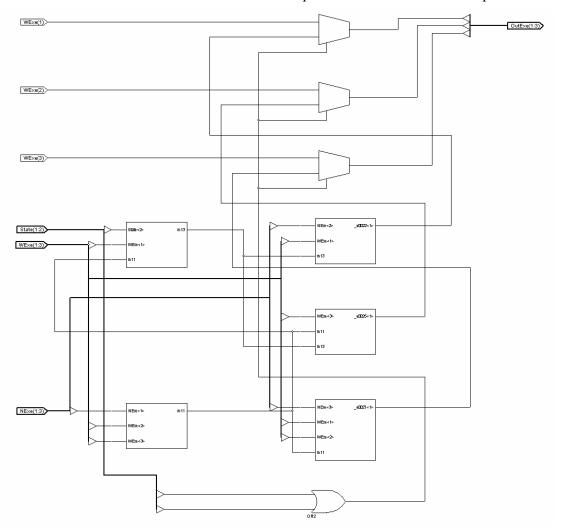

| Figure 7-1 3x3 Cells Digital Organism                                                  | 92    |

| Figure 7-2 Distribution of states                                                      | 95    |

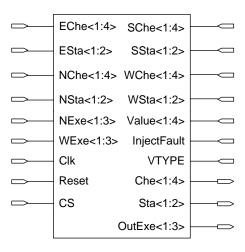

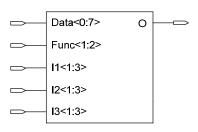

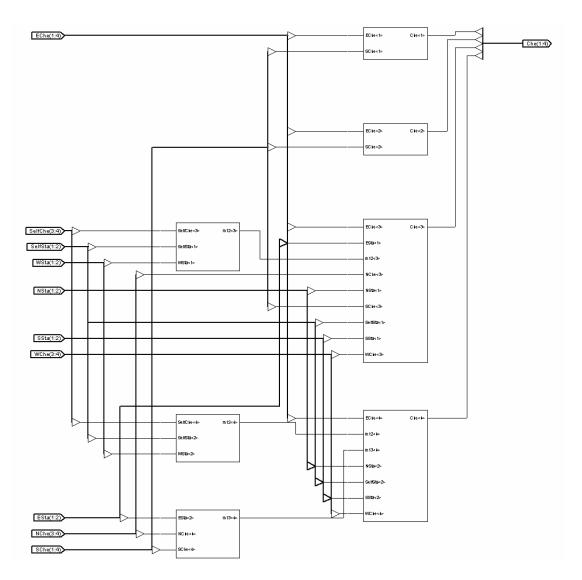

| Figure 7-3 Digital Organism External Interface                                         | 96    |

| Figure 7-4 Digital Cell External Interface                                             | 97    |

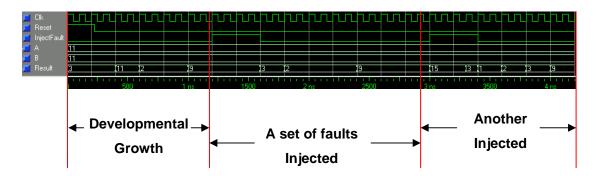

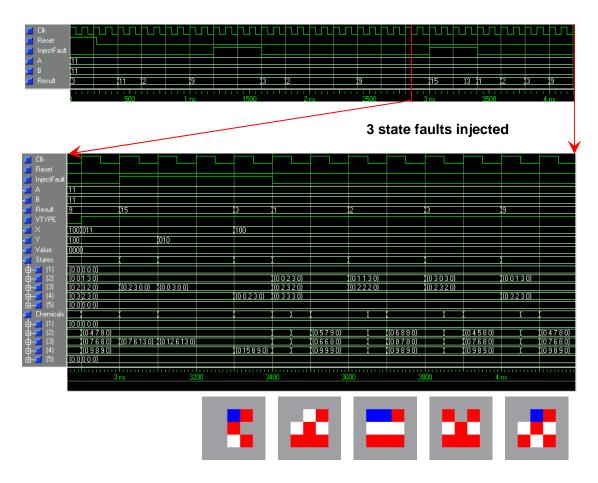

| Figure 7-5 Overview of the Simulation Waveform                                         | 98    |

| Figure 7-6 Developmental Growth Procedure                                              | 98    |

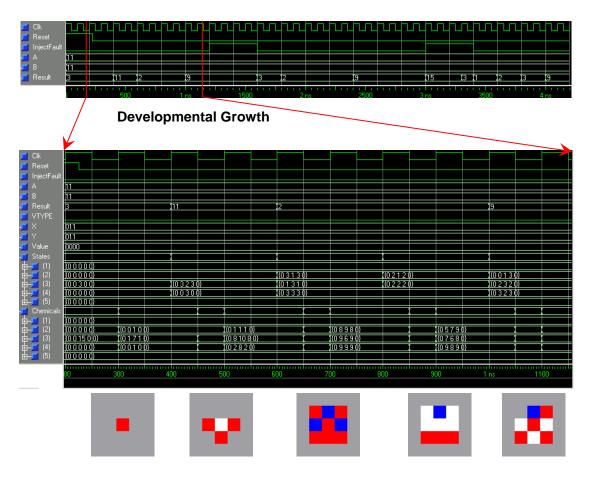

| Figure 7-7 Injection of the first set of faults and the recovery procedure             | 99    |

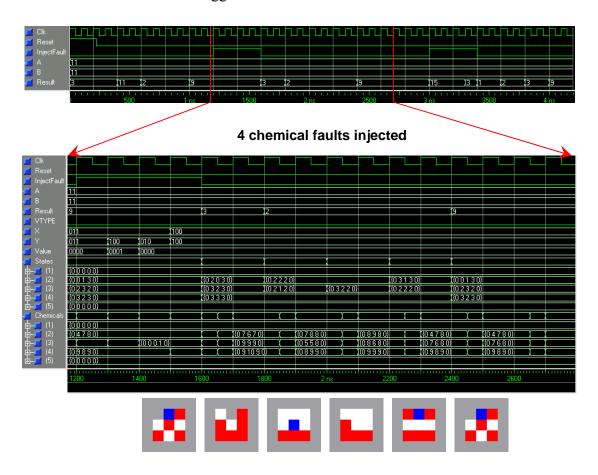

| Figure 7-8 Injection of the second set of faults and the recovery procedure            | .100  |

| Figure 8-1 Molecule Interface                                                          | .104  |

| Figure 8-2 The Architecture of Molecule                                                | .105  |

| Figure 8-3 Top-level Overview of the Intrinsic Evolvable Hardware Platform             | ı 107 |

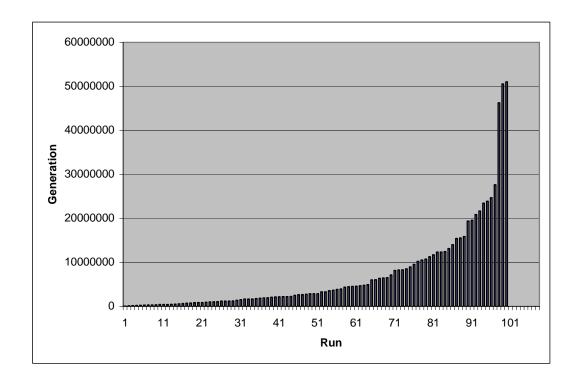

| Figure 8-4 The distribution of the generations of the 100 experimental runs            | .114  |

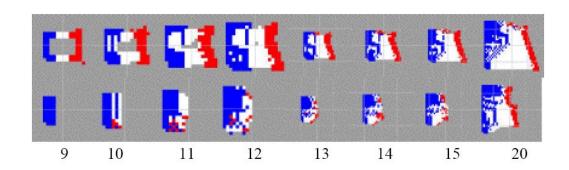

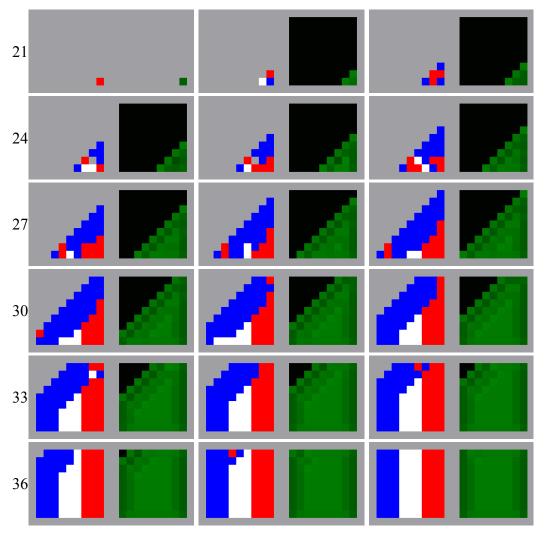

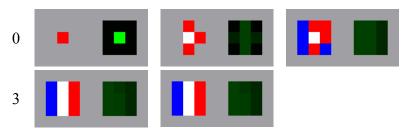

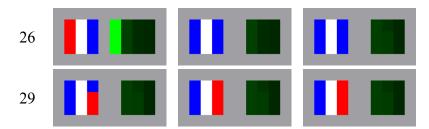

| Figure 9-1 Adaptive French flag grows to maturity                                      | .117  |

| Figure 9-2 Adaptive French flag recovers from a set of transient faults                | .117  |

## Figure Index

| Figure 9-3 The flag transforms to "inverted" flag to adapt to the environn signal |     |

|-----------------------------------------------------------------------------------|-----|

|                                                                                   |     |

| Figure 9-4 Inverted flag recovers from transient faults                           | 118 |

| Figure 9-5 Re-grow to French flag after resetting environmental signals           | 118 |

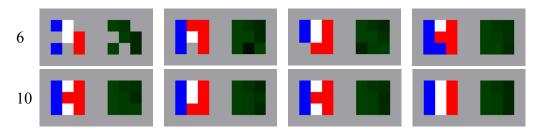

| Figure 9-6 1-Bit RAM Growth                                                       | 120 |

| Figure 9-7 1-Bit RAM Recovery from faults with value 0 saved (default)            | 120 |

| Figure 9-8 1-Bit RAM Stores 1 as its new value                                    | 121 |

| Figure 9-9 Saving 0 to 1-Bit RAM when 1 is stored                                 | 121 |

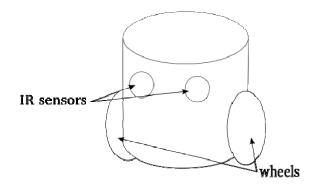

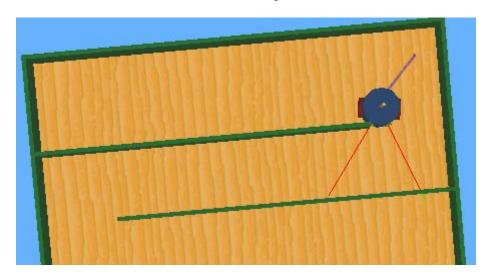

| Figure 10-1 Kiki robot                                                            | 126 |

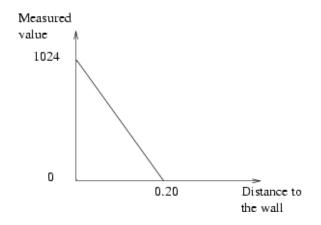

| Figure 10-2 Distance measurements of the Kiki sensors.                            | 127 |

| Figure 10-3 Simple environment                                                    | 128 |

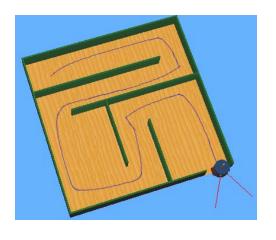

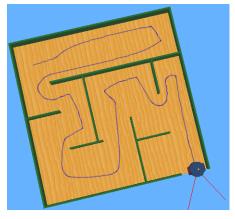

| Figure 10-4 Maze environment                                                      | 128 |

| Figure 10-5 3x3 Cells Digital Organism for robot controller                       | 130 |

| Figure 10-6 Kiki robot                                                            | 130 |

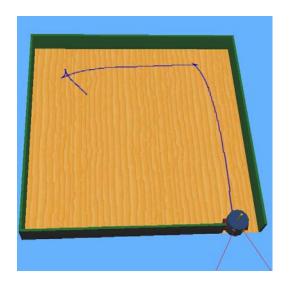

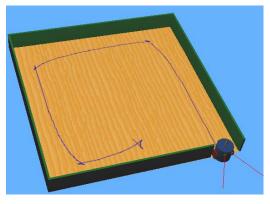

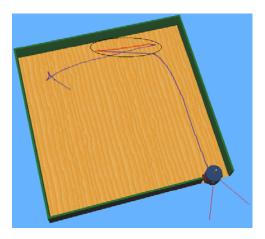

| Figure 10-7 Trajectory of Kiki for the simple world                               | 131 |

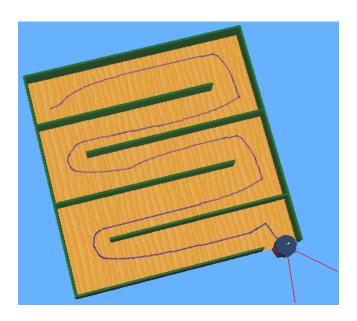

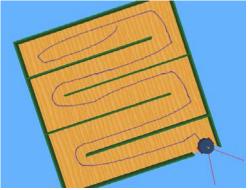

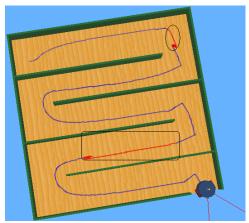

| Figure 10-8 Trajectory of Kiki for the maze world.                                | 131 |

| Figure 10-9 Trajectory for the simple world with different starting point         | 132 |

| Figure 10-10 Trajectory for the maze world with different starting point          | 132 |

| Figure 10-11 Trajectory for the simple world with faults                          | 132 |

| Figure 10-12 Trajectory for the maze world with faults                            | 132 |

| Figure 10-13 A case where the simple controller fails                             | 133 |

| Figure 10-14 New maze world 1                                                     | 133 |

| Figure 10-15 New maze world 2                                                     | 133 |

| Figure 10-16 The maze controller fails when the wall is not detected              | 134 |

# **Table Index**

| Table 2-1 Differences between the four types of EA                | 18       |

|-------------------------------------------------------------------|----------|

| Table 3-1 Biological Cell Components and their functions          | 28       |

| Table 3-2 Definition of Lindenmayer's L-system for algae growth   | 33       |

| Table 3-3 The Production of Lindenmayer's L-system                | 34       |

| Table 4-1 some well known Fault Types and their classification    | 47       |

| Table 4-2 Ratios of transient errors to permanent failures [66]   | 48       |

| Table 5-1 A 3x3 Digital Organism.                                 | 62       |

| Table 5-2 Comparison of Biological Cell with Digital Cell         | 67       |

| Table 6-1 Growth speed comparison of this proposed model (left)   | with Dr. |

| Miller's model (right)                                            | 84       |

| Table 7-1 Available functions for Molecules                       | 94       |

| Table 7-2 Overview of states occurrence in first stage experiment | 95       |

| Table 7-3 Chosen Cell State Pattern                               | 95       |

| Table 7-4 Resource Consumption of the Digital Organism FPGA       | VHDL     |

| implementation                                                    | 101      |

| Table 9-1 General RAM Memory Interface                            | 119      |

| Table 9-2 2-bit and 3-bit RAM Unit Experiment Results             | 123      |

| Table 10-1 Dimensions of Kiki Robot                               | 127      |

| Table 10-2 Wheel speed decoding schema                            | 129      |

## **Chapter 1**

# Introduction

Electronic systems are so used to by modern people in our everyday life that little attention is paid to them. However, they are utilized in almost every aspects of our society: from normal telephone to high-definition television, from smart mobile phones to most advanced cars, electronics systems coordinate all the components to work for the purpose.

Electronics systems do not only improve the convenience, efficiency and effectiveness of our daily life, they also help us achieve "impossible missions": they allow us to dive into hazards deep sea, to explore on the surface of Mars and to make a long journey to the deep outer space for extraterrestrial intelligent cultures.

With the development of electronic technology, more complex and larger systems are designed and this tendency shows no sign of decelerating.

However, in spite of the achievement of designing complex systems, the resulting systems may not be as efficient as expected in regards to general robustness to system faults and adaptiveness to unpredictable changes in operating environments. Several factors contribute to these limitations. One of the most significant points is that all these systems are designed explicitly to a preset environmental condition. If either the specification for the system is difficult or even impossible to define, or the entire combination of environment conditions is unpredictable, the conventional design methodology may be more prone to lead to defective behaviour. The failure of Beagle 2 project [78] was led to by the very issue: the estimation of the atmosphere in Mars was not accurate; the surface characteristics in the landing site were little known; all landing conditions can not be predicted, and Beagle 2 was stuck in one of the un-foreseen scenarios. [79]

One the other hand, the most complicated systems existing on this planet, humans, are *created* by nature: from the development of a single cell to an adult, the blueprint to build a human has enough error margins to cope with

#### Chapter 1 Introduction

unpredictable environments correctly. In addition, human can adapt to the changing environment efficiently.

As a matter of fact, most living multi-cellular biological organisms exhibit these intrinsic characteristics electronic engineers earnestly long for. Amphibians can regrow lost limbs [82]; Mice can repair their punched ear very quickly and without scars [80]; Human can regenerate their liver throughout their whole life time [81].

Multi-cellar living organisms achieved these traits through millions of years of evolution by means of cells which have identical genotypes. In most cases, all of them come from a single special cell (zygote): this process is called development. The entire process of development is controlled by the interaction of cells rather than by a centralized process.

Evolution is the approach of nature to *design* complex living creatures. Evolution refers to the process in which beneficial traits are inherited from generation to generation. Varieties of traits are generated by genetic drift, such as mutation, genetic recombination, sex and gene flow. Among these novel traits, only the ones increase the survival chance of the individual will be passed on to next generation. This is called the natural selection. In other words, it is determined by natural selection that whether a particular characteristic is beneficial or not [83][84][85]. Although new species occurrence normally takes long stretches of time, it is suggested that evolution rate can be seven orders of magnitude greater than rates implied by the paleontological records [86].

One approach to tackle the issues raised previous about designing electronics systems is to draw inspirations from the biological systems to design novel frameworks.

The most widely used methodology in bio-inspired research areas is evolutionary algorithm, which mimics the biological evolution. Evolutionary algorithm will be discussed in further details in Chapter 2.

In this chapter, basic background and motivation of this project is overviewed first; following that, the hypothesis is presented; achievements of this research is highlighted in section 1.3; finally the structure of this thesis is reviewed.

## 1.1 Research Motivation and Objective

In order to try to discover novel approaches to overcome the shortcomings of existing design methodology, the project draw inspiration from development principle to design novel frameworks.

Although development principle <sup>1</sup> has been applied to various electronics models to obtain emergent properties, most of them tend to rely on the explicit information about the positions of cells in the cell array: the position of a cell may be fed to each cell or configured within the genotype. In addition, most of work in this field only deals with applications with no real world functionalities, such as pattern formations.

In this research, we will provide a developmental model which does not depend on any knowledge about cell coordination. Evolution is deployed to generate the desired design for a particular application, thus we also deliberate the requirements for evolving with such a developmental model. We will also describe how to deploy this model so that it can be applied to evolve functionalities, such as multipliers and robot controllers

In traditional evolution encoding schema, the solution of a specific system is encoded entirely in the chromosome so that it can be mapped directly to the result. Despite its simplicity and wide acceptance, it is not particular suitable for multi-cellular model due to the fact that the data the chromosome needs to contain is proportional to the number of cells (components) in a system.

In addition, the conventional evolution algorithms does not provide any mechanisms to honor the complicated interaction between sub-components in the system, as the case in the biological development which is facilitated the gene regulation network: the dynamics of the development model can not be exploited which could lead to fault-tolerance features or dynamic modification of the organism, as they make use of static mapping between genotype and phenotype.

<sup>&</sup>lt;sup>1</sup> Biological development principle will be reviewed in Chapter 3.

Therefore a novel evolutionary algorithm tailored for hardware implementation and the grow mechanism are developed. (discuss on multiple chromosomes in conclusion/future section)

To summarize, the objective of our work is to propose a general FPGA-based evolutionary developmental model, which has the emergent properties of adaptation and fault-recovery and can be deployed to incorporate various functionalities.

## 1.2 Hypothesis

Our hypothesis for this research is: a system model derived from developmental principles can lead to emergent properties of adaptation and fault-recovery which can achieve levels of reliability for hardware systems, and functionality can be incorporated to development systems to perform desired functions.

### 1.3 Achievements

This section provides an overview about the achievements of this research, including references to the relevant chapters with more details.

We propose a developmental model<sup>2</sup> inspired on its biological counterpart<sup>3</sup>, in which an indirect genotype and phenotype mapping in the form of a simplified development process is deployed. This model is designed with hardware in mind so that it can be accomplished and executes efficiently in hardware implementation. In order to demonstrate some of the emergent features of this model, we first present the evolution and development of a French Flag assumed by the model (Chapter 6), which is a pattern formation problem with a French Flag pattern as the goal. Notably extremely high capacity of transient fault tolerance is observed.

After introducing the characteristics of the model, we then let it to carry some functions: the model is employed to implement a simple digital logic circuit (2 bit multiplier), and realized it in an off-shelf FPGA. We show that this model is

\_

<sup>&</sup>lt;sup>2</sup> The model is discussed in detail in Chapter 5.

<sup>&</sup>lt;sup>3</sup> In section 3.1, the biological principle of development is review.

indeed hardware friendly and the high performance of hardware implementation compared to software simulation (Chapter 7 and Chapter 8).

As the model equipped with memory units, sequential circuits are investigated in Chapter 9, where the model is enhanced and fine tuned. We demonstrate that the model can be used not only for combinational digital systems, but also for circuits with memory.

Finally in Chapter 10 we evolve autonomous robot controllers to control the navigation of a robot, which is a more chanllenging problem then multiplier. We demonstrate the capacity of the model in solving non-trivial applications with the bonus of implicit fault-tolerance and self-repair.

#### 1.4 Structure of the Thesis

This chapter presents the necessary introduction information for this work. In the following chapters, we will first review the evolution methodology in electronic system design in Chapter 2. We introduce the definition of evolutionary algorithms and evolvable hardware. We discuss the latter one in further details with digital and analogue system evolution and the clarification of evolvable hardware.

Since this research draws the inspiration from biological development principles, we brief the biological background in Chapter 3. Some existing computational abstractions of the principles are examined as well. At the last of this chapter, we present some development models proposed to work with electronics systems and we also review their applications.

Next we introduce the definition of fault-tolerant techniques in Chapter 4. We begin with basics concepts and definitions. Then the evolution of fault tolerance systems is described and conventional techniques are examined. We also present fault tolerant techniques inspired by different principles from biology.

In Chapter 5, we present the developmental cellular model proposed in this work. We show the process of the transforming from biological principles to digital circuits and systems. The internal structures of the model and the chemical diffusion mechanism are described first. The growth strategy deployed and the genotype representation of the digital organism are the highlighted. One

#### Chapter 1 Introduction

of the novel contributions of this thesis is to introduce an execution unit which brings functionality to developmental systems.

We reveal the built-in fault tolerant features of the simplified developmental model in the French Flag software simulation in Chapter 6. An evolutionary algorithm employed in this research is first presented which specifically fine tuned for hardware implementation. Then we demonstrate the setup of the experiment and the findings about the recovery characteristic of this model in the ending part of this chapter.

After incorporating all the components in the model, we present the implementation of a simple digital logic circuits assumes by this framework in Chapter 7. Details and results about both software simulation and intrinsic hardware implementation on FPGA are described.

In Chapter 9, the model faces a new challenge to deal with a sequential system, which is the fundamental infrastructure for learning. We first introduce adaptive behaviours and attempt to adapt the model for adaptive traits. Then we move on to evolve memory with more capacities.

A more complex application is evolved utilizing the model in Chapter 10, autonomous robot controller. The definition and background about robot controller are reviewed and then the configuration of the experiments is presented and results are discussed.

Finally, in Chapter 11 we conclude this thesis with emphasizing on contributions of this project, and make suggestions about further potential research directions.

# **Chapter 2**

## **Evolutionary Design of Electronic Systems**

As the basis of the evolution theory in biology, natural selection was first set out by Charles Darwin and Alfred Russel Wallace [133], the idea of which is that it is more likely for individuals who possess inheritable advantages to survive and more importantly to replicate. Inheritable advantages refer to capacities of tackling challenges posed by their own biological body and external ecological and physical environment. In modern evolution theory in biology, called the modern evolutionary synthesis, it is known that these advantages are encoded in the form of genes in DNA and these genes can be passed on from generation to generation. [87]

Some search and optimization techniques are inspired by natural evolution theories. These techniques are normally called evolutionary algorithms which can be deployed to design electronics systems. This chapter gives an overview of the evolutionary design approaches employing evolutionary algorithms. It presents the principles of evolution of electronics systems and introduces the evolutionary algorithms. Finally, this chapter highlights the discipline of evolvable hardware and discusses its applications in both digital and analogue systems.

## 2.1 Introduction

Inspired by the design approach of nature, evolution, similar methodologies were proposed to create artificial evolution for computational and electronics applications to explore novel solutions or optimize existing implementation. A common trait among these approaches is the utilization of evolutionary algorithm [23] [39], which refers to a generic search and optimization paradigm inspired by biological evolution in the form of simulating natural evolution over populations of candidate solutions. Specifically, the employment of evolutionary algorithms to design hardware electronics systems, such as circuits and controller structures, is called Evolvable Hardware (EHW).

The earliest citation of the EHW idea may come from Turing in 1940s. He proposed a network of unorganized randomly inter-connected NAND logic gates [88]. This primitive machine may be the first "neural network" system. He also suggested that it would be possible to make use of evolutionary search to train the network. However he did not actually investigate it further.

The concept of EHW was first conceived by H. De Garis in 1992 to accelerate trainings of neural network. The common definition of EHW was then introduced by Higuchi in 1993 after hearing H. De Garis's talk on the EHW idea [89]. Higuchi accurately foresaw EHW as an emerging new branch of Artificial Intelligence and "the basis for a radically new approach to electronic and computer design" [90].

From the authors' point of view, Evolvable hardware is the deployment of evolution design approach, specifically evolutionary algorithms, to meet all the requirements a predefined objective purpose. The key points in this definition are that the targeted application has to be implemented in hardware finally and evolutionary algorithms are utilized to obtain the desired functionality, the internal structures of the system and the inter-connection of the building blocks.

The final hardware can be assembled from discrete components, such as logical gates, shifters and latches. Alternatively, nowadays there are wide ranges of reconfigurable devices which are capable of implementing complex applications, so EHW may take the form of reconfigurable devices as well.

One of the advantages of the evolvable hardware approach over traditional design method is that it can be applied to application with only high level specifications: identifying the objective is easier than specifying the implementation particulars. Taking robot controller for an example, it is difficult to determine whether a particular output from the system is superior to another directly without feeding the output to the activator of the robot. On the other hand, we can distinguish how well a controller is doing when it is manipulating a robot in an environment. In addition, the design of the controller itself is automated by the employment of evolutionary process.

We present the principles of evolutionary design methodology first in section 2.2. Various well established evolutionary algorithms are overviewed in the next

section 2.3. More details about evolvable hardware are discussed in section 2.4, which includes highlights of existing evolved digital systems, as well as analogue counterparts. In the last section 2.5, we conclude this chapter with summarizing the approach we were followed in this research.

# 2.2 Principles of Evolutionary Design

Figure 2-1 Flow Chart of Evolutionary Design<sup>4</sup>

Applying the evolutionary design methodology is quite different from the conventional approach. First of all, it normally requires selecting the building blocks or components available to the evolutionary algorithm to explore, and the interconnection structures between these parts. Second, a genetic representation of the solutions should be defined which is capable of describing what building blocks to deploy and how to connect them. Afterwards, a *fitness* function should be designed to evaluate how well a solution encoded in the genetic representation is doing at accomplishing a specific task. Eventually, the evolutionary algorithm generates a pool of potential solutions encoded in their genetic representation and operates on them with the objective of augmenting the best and overall fitness of

<sup>&</sup>lt;sup>4</sup> The procedure "Execution of Evolutionary Algorithm" is demonstrated in Figure 2-5

the population. When a system is created by an evolutionary algorithm, we call the system is *evolved* (see Figure 2-1), rather than *designed* specifically as in the traditional approach.

On the contrary, conventional hardware design procedure generally consists of writing functionality specification, synthesising an abstract implementation, implementing each components or sub-systems and testing of the final design.

Figure 2-2 Conventional Circuit Design Flow

In Figure 2-2, a typical traditional design flow of circuits is depicted. It demonstrates that it is necessary to specify the lowest level of details of the implementation in this design methodology.

There are several methods of describing the abstract implementation. The most historical representation is schematics. An electronics schematic is a brief diagram of a circuit. It includes simplified and standardized pictogram of components used in the circuit and the connections between these components and power supply. The components could be logic gates or integrated chips, or a block representing another schematic.

Graphic representation of abstract implementation of Finite State Machines (FSM) includes state diagrams and state transition tables. A FSM or Finite Automation is a model of a behaviour defining possible states of a system, transitions between states and actions which trigger transitions. State diagrams represent these three key elements in a graph, while state transition tables

describe what state to move to given a combination of input and current state in tables.

With advancement in electronic technology, other representations of abstract implementation are introduced. For instance, Hardware Description Language (HDL) is essential for modern digital system design with explosive complexities. HDL is a textual representation of a system. HDL describes the operation and design of hardware as programming languages describe a piece of software. HDL may describe structures composed of basic logic elements, such as logic gates, and hierarchical custom modules.

Figure 2-3 Simplified PLD Structure The structure for one output pin [146]

Recently, reconfigurable devices are becoming more and more popular due to its fast prototyping nature. These devices can be reconfigured after manufacture and tailored for specific tasks using HDL or schematic design. The first device of reconfigurable device introduced was Programmable Logic Array (PLA) which can achieve combinational circuits (see Figure 2-3). Any Boolean logic function can be denoted by a sum of product terms (sum-of-product), the structure of PLD is sum-of-product oriented which makes it efficient to implement such circuits. Each output of PLD is from an OR gate which acts as the sum operation. The inputs to the OR gate are determined by configuration. Each horizontal line connected to the OR gate is an input, and represents an AND gate. The inputs to each AND gate are programmable, and include input signals, their inverse or remain unconnected. In Figure 2-3, a black dot in the horizontal line represents a connection between the input signal and the AND gate, while a white dot means

no connection of the two crossover lines. In the figure, the upper horizontal line (AND gate) connects to inputs I0 and I2 (I0 • I2), while the lower AND gate connects to input I1 only. As a result, the output = I0 • I2 + I1. The connection in the configurable AND gates are one-time programmable fuses or reconfigurable memory based element. These configurations can be considered as the genetic string for the circuits.

Programmable Array Logic (PAL), a form of improved PLA, was then announced which is capable of implementing simple sequential circuits. Afterwards, Complex Programmable Logic Device (CPLD) based on macro cells was introduced which provides more capacities in terms of available logic units.

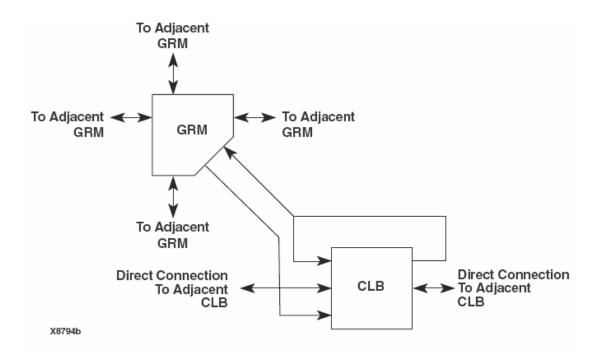

Figure 2-4 Typical Configurable Logic Block Architecture

With the announcement of Field Programmable Gate Array or FPGA, reconfigurable devices are brought to a new high level. FPGA features not only configurable components, but also customizable inter-connections. FPGA includes a larger number of programmable logic elements so it can even incorporate more complex systems, such as CPU cores. Although FPGAs from different vendors are different from each other substantially, they share the typical basic structures. The classic architecture comprises an array of configurable logic blocks (CLBs) and routing resources (routing channels). Each row or column of the CLB array may have more than one Input/Output pad fitted. The typical CLB structure is demonstrated in Figure 2-4. It consists of a 4 input look-up table (LUT) and a flip flop. Output from a CLB is only one bit: it can be either the output of the LUT or the flip flop which is controlled by a configuration bit. The content of LUT is also specified by the configuration string. The output can connect to routing channel below and the channel to the right. The routing channels are normally segmented: routing wires are connected

by configurable switch boxes. By default, switch boxes are not connected, while configuration string can program switch box to connect adjacent routing wires.

Reconfigurable devices for analogue systems are also available, called Field Programmable Analog Array (FPAA), which typically are composed of operational amplifiers, programmable capacitor arrays and programmable resistor arrays or configurable switches for switched-capacitor circuits.

In evolvable hardware, genetic encoding can take all of the above forms, such as HDL or an index graph of schematics. However, these representations are tending to be executed in software simulation rather than in hardware directly, due to the fact that the transformation from abstract implementation to hardware is computational intensive. Alternatively, the generic encoding can be the native form as the configuration format (normally a string of binary) of a device, such as FPGA, so that it can be downloaded to the device to assess the fitness directly.

FPGA is particularly popular in evolvable hardware community due to its highly reconfigurable architecture. In addition, the various configuration approaches to customize the device contribute to the popularity, including HDL, schematic design and native configuration string. The emergence of FPGA makes it possible to execute complex algorithms online with fast implementation methods, thus FPGA is one of the most ideal platform for evolvable hardware.

# 2.3 Evolutionary Algorithms

Evolutionary algorithm is one of the most significant components in the evolutionary design methodology which mimics the natural evolution with selection and differential replication procedures. Various forms of evolutionary algorithms have been proposed and investigated. Some of the most representative classes of evolutionary algorithm are considered to be *genetic algorithms*, *evolutionary programming*, *evolution strategies* and *genetic programming* [22] [25] [40].

#### 2.3.1 Common Features

Although these four varieties of EA are proposed for different purposes, they all share several common properties.

One common feature of these algorithms is the use of population. A pool of candidate solutions to the specific task is usually referred to as a population of individuals.

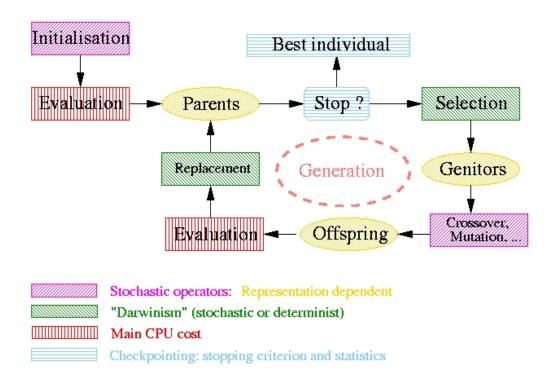

Another characteristic shared by all the EAs is that it requires a scalar *fitness* measurement to evaluate the performance of a particular individual in the population to satisfy the targeted problem. In each iteration the fitness of all individuals is calculated. If the predefined stop criteria are met (normally it is in regards to the best fitness), then the EA stops. Otherwise, it selects some (in some cases all) of the individuals to replicate. Just as in nature, no two copies are exactly the same; the duplication procedure in EA also applies genetic variation operators. The common flow chart for EAs is shown in Figure 2-5.

Figure 2-5 Flow chart of common EA

Before start of EA, an initial population is generated (see Figure 2-1). The fitness for all the individuals in the population is evaluated first. If stop criteria are not met (stop criteria normally are set as target fitness or number of generation), new population is generated by applying genetic operators and it loops back to evaluating individuals. Otherwise, if stop criteria are satisfied, EA exits.

Mutation and crossover are the most popular genetic operators in the community. Mutation involves modifying a part of the chromosome to generate a new offspring, while crossover generates new generation by combining parts of chromosome from (normally) two parental individuals. These reproduce

offspring forms the next generation and are exposed to the same selection procedure if stop criteria are not satisfied.

In evolvable hardware context, binary encoding and its derivate are widely used. In Figure 2-6, the mutation normally deployed in binary encoding EA is demonstrated. In the resulting chromosome (on the right hand side of "=>"), the bold digits are the modified bits by the mutation operator. Mutation only requires one and only one individual to generate one offspring.

Figure 2-6 Mutation in Binary Encoding EA

Figure 2-7 Crossover in Binary Encoding EA

On the other hand, crossover can have several forms. In Figure 2-7, four types of crossover operators are illustrated. Crossover requires at least two individuals (parents) to generate one or two offspring. In single point crossover, one point in the parents is selected, and one part is exchanged between the two parents to

generate to two new offspring, while in two-point crossover, two points are selected and the part between the points are swapped between the two parents. Other two types of crossover are also demonstrated in the figure. In uniform crossover, each bit in the offspring is selected randomly from the two parents. The bold digits are the selected ones. Another possible crossover operator is arithmetic based: the resulting offspring is generated by an arithmetic operator, such as XOR, AND, performed on the two parents.

Spears compared the relative importance of crossover and mutation in [134]: "Mutation serves to create random diversity in the population, while crossover serves as an accelerator that promotes emergent behaviour from components. The meta-issue, then, is the relative importance of diversity and construction. For the GA community, this is also related to the balance between exploration and exploitation." It is suggested that mutation plays more important role than crossover in population with less diversity. It is also argued that the difference between mutation and crossover is not as obvious as it seems, and they can be considered as two extreme forms of a general genetic operator.

As for evolvable hardware, due to the resource constraints, population is limited and as a consequence the diversity in the population is normally relatively low. Thus mutation should have more impact in the EA than crossover. In addition, mutation is easier to implement than crossover. In this thesis, only mutation operator is employed.

The word *mapping* is often used in EHW to depict the decoding procedure from chromosome to the actual presentation (from genotype to phenotype).

#### 2.3.2 Overview of EAs

Genetic Algorithms (GAs) were originally proposed to explore the adaptive systems principles [26] - [28]. It encodes the parameters of a system as bit strings which consist of genes. A gene is considered to be several bits representing a single parameter. As each gene is the direct binary representation of a parameter, it is straightforward to apply the chromosome to hardware. Generally, GAs make use of both mutation and crossover. Random bit flip is deployed as mutation, while exchanging sub-strings is used as crossover mechanism. The split of genes

is arbitrary and it can encode any parameters, which makes it a universal optimization technique for complex systems.

On the other hand, Evolutionary Programming (EP) was intended to carry out intelligent behaviour simulation using Finite State Machines (FSM) [29] [30]. They normally take the form of two functions, first of which represents the transition subject to a given combination of current state and inputs. The other function defines the outputs in a particular state with a set of inputs. Genetic variation operators can modify the available states and the transition between them. Outputs of the FSM can also be changed.

Similar to GA, Evolution Strategy (ES) was originally designed to be a parameter optimization method for aero technology devices [31] - [34]. However, rather than encoding the parameters in their binary forms, ES makes use of the parameter directly. It maintains a list of value pairs: the first one is the object parameter, which is the target to be optimized, while the second one is the strategy parameter which controls the mutation rate of the corresponding first value. The mutation of the first value in each pair is performed by adding a normal distributed number with the deviation given by the second value in the pair. The strategy parameter is mutated by randomly increasing or decreasing the value. Crossover is carried out by selecting each pair from its two parents with 50% probability. When the presentation of a task is a list of numbers, ESs are sometimes used in EHW.

Figure 2-8 GP Genotype Demonstration

Genetic Programming (GP) was developed as an automated method of finding a "program" to solve specific problems [35] [36]. The original GP is a multi-branches tree (see Figure 2-8). The leaves of the tree are the input parameters, while each node is a function which operates on the branches it connects to. The result of the node is passed further on the branch to its parent as an input. The

result of the root node is used as the output of the system. Mutation and crossover operators specific to GP are designed. Mutation can modify the function of nodes and the value of leaves. Crossover can chop a branch and clone one from another parent.

#### 2.3.3 Comparison of different EAs

The essential difference between these four types of EAs relies on the different chromosome representation. Due to the diversity of the encoding mechanisms, the genetic operators are also specialized for each kind of EA (see Table 2-1).

In general, EAs belong to the population based family of search and optimization. There are some other related techniques, such as simulated annealing (SA) [91][92]. Rather than inspired by biology, it is modelled after annealing in metallurgy. It normally only has one individual in a population. In each step, the current individual is replaced by a random solution, determined with a probability that relies on the current fitness and a global parameter (called temperature T). T is gradually decreased, so that at the beginning the new solution is generated almost completely randomly when T is large, while it converges to the global optimum as T goes to zero.

|    | Represen-<br>tation | Genetic Operators   |                    |            |

|----|---------------------|---------------------|--------------------|------------|

| EA |                     | Mutation            | Crossover          | Other      |

| GA | Bit Strings         | Bit flips           | Substring exchange |            |

| EP | Functions           | Changing transition |                    | Add or re- |

|    |                     | rules/output        |                    | move stats |

| ES | List of value       | Adding a random     | Uniform Crossover  |            |

|    | pairs               | number              |                    |            |

| GP | Tree-like           | Change the value or | Subtree exchange   |            |

|    | structure           | function of a node  |                    |            |

Table 2-1 Differences between the four types of EA

In [93], EP, ES and GA were compared against a set of different parameter optimization problems. It is suggested that, as their main design purpose, EP and ES are more suited for parameter optimization. GA is more oriented for general problem evolution. It is also found that because of its self adaptation of mutation rates, ES can converge more quickly than GA.

In this project, genetic programming was employed to search for solutions of the problems presented. The deployed GP will be discussed in further details in section 5.6.

#### 2.4 Evolvable Hardware

When evolutionary algorithms are applied to the implementation and/or design of hardware, such as electronic circuits [24], we can realize evolvable hardware (EHW) [43].

The first possibility of EHW was brought to us by the Programmable Logic Array (PLA) devices. Nowadays, more complicated and higher density Field Programmable Gate Arrays (FPGA) are available in reasonable prices, which provide an ideal platform for EHW.

In this section, we introduce several existing classification of EHW first. Afterwards, we focus on a particular type of classification and present previous research projects and their achievements.

#### 2.4.1 Classification of Evolvable Hardware

Based on different criteria, different classification systems are conceived. In general, two types of classification are used.

In regarding to where the evolutionary algorithm and the evaluation of individuals are implemented, there are two methodologies of EHW [44][45]. One is Extrinsic Evolvable Hardware (EEHW) [57] - [60], the other is called Intrinsic Evolvable Hardware (IEHW) [42] [47]- [55]. As the name indicating, in the former type of EHW the EA is realized in a computer (i.e. software) as well as the evaluation of each individual and the elite solution is then implemented on the hardware, while in the IEHW case the EA is carried out at least partially (possible completely) in hardware. In this thesis, two sub types of IEHW are defined: full-IEHW and semi-IEHW. The former term refers to systems in which evolutionary process and the evaluation of population are completely independent from the host PC, meanwhile the latter one refers to these which only parts of the system (the evaluation component for instance) are realized on the hardware.

EEHW is relatively straightforward to implement comparing with IEHW, because the EA is implemented in software program. However, IEHW has an advantage over EEHW in that in general hardware is much faster than software simulation, especially with regard to evaluating digital circuits. Also it allows physical characteristics of the system to be part of the evolutionary process. An EEHW will be presented in Chapter 7 and an IEHW will be discussed in Chapter 8.

Another popular system classifying EHW depending on whether any constrains are imposed in the possible hardware configuration. In intrinsic evolvable hardware, if the encoding of the problem can access all possible configurations of the underlying hardware without any limitations, then this is *unconstrained* EHW. This technique can explore unknown characteristics of the fundamental hardware and materials (normally silicon) of the hardware.

There is another not so popular classification system, which divides EHW depending on whether the evolutionary algorithm is realized in a chip or in the computer, and termed them as *on-chip* and *off-chip* EHW [94].

#### 2.4.2 Extrinsic Evolvable Hardware

Considerable efforts have been devoted to the EHW research field. Due to the relative simplicity of EEHW, most of the research carried out is in the extrinsic area.

EHW can result in novel implementation of well known functionality. Miller successfully evolved 6 tap digital finite impulse response (FIR) filters with only multiplexers as building blocks [143]. Cartesian Genetic Programming (CGP) (see section 5.6) was utilized to encode circuits [4]. An array with 7x7 logic elements was employed to achieve the target FIR filter. The evolved circuits are fed with sample signals and the fitness is evaluated by the output similarity to the desired filtered signal. Individuals that displayed the targeted band-pass filtering behaviour are evolved successfully. It was observed that no explicit of multiplications or additions were in the evolved circuits. It was emphasised that no known mathematical way to implement a FIR filter with only multiplexers. This approach can be referred to as schematic evolution, in which a representation of circuits is evolved.

Figure 2-9 Circuit Representation in Miller's work

The two inputs of each gate (square block in the figure) can only connect to the outputs of its left columns of gates [144]

Schematic evolution can also lead to novel implementations with fewer resources than human designed solutions. Miller et al. evidenced this by evolving 1x1, 2x2 and 3x3 bit multipliers using CGP which require less two-input gates than the best known conventional design [144]: a 3x3 multiplier implemented with 21 gates (14 two-input gates and 7 MUX) was evolved, while the most efficient conventional design requires 26 gates (24 two-input gates and 2 MUX). (see Figure 2-9)

In [150], Kumar et al. proposed a *virtual reconfigurable circuit* (VRC) on top of normal FPGAs. The VRC is composed of *processing elements* (PEs), each of which can be configured to perform a certain binary functions. PEs are interconnected as shown in 10: there are 25 PEs, with 24 are laid out in a 4x6 matrix and the remaining one as the output PE. All PEs in a column can only connect to outputs of PEs located on the 2 columns on the left. A PE has 2 8-bit inputs and one 8-bit output, and it may have one of 16 possible binary functions. They successfully evolved an image filter which outperforms conventional human designs: the evolved filter can obtain better images from distorted original images then human designed filters. The VRC can be translated to a CGP encoding straightforward: with a 4x7 molecules of CGP, specifying one of the molecule on the right most column as the output.

Figure 2-10 Architecture of VRC [150]

More recently, Masiero et al. looked at how to deploy EHW to solve designing issues in a merging field: molecular circuit. Rather than trying to build smaller components of circuit, this novel approach is to use individual or a small collection of molecules to achieve computational functions, such as AND gate [140]. They designed a SPICE model to simulate molecule level logic gates and employed EHW to integrate basic gates to form diodes. They demonstrated that, with the help of EHW, building blocks of molecule circuits can be achieved. This demonstrates that how EHW can be helpful to achieve novel designs.

All these researches mentioned above demonstrated that, with the help of EHW, it is possible to obtain novel designs which can be superior or more resource efficient than human designed solutions. Thus EHW was chosen as an ideal methodology to explore novel designs in this thesis.

#### 2.4.3 Intrinsic Evolvable Hardware

Despite of being more sophisticated than EEWH, more and more resources and endeavours have been being invested into IEHW systems to obtain more superior performance.

FPGA, the ideal platform for IEHW, makes use of binary strings to configure its functionality and intra-connections. However, with some FPGAs, not all possible combinations of configuration binary strings will yield a working circuit.

In Fact, some of these configurations can even permanently damage the hardware [46]. One way to avoid that is to only modify a valid design [46]: a 8-bit counter was successfully evolved using this method. In [47] Smith et al. followed a similar route: a secure intrinsic abstract layer was presented for Virtex FPGA which basically mimics a XC6200 FPGA that can not have harmful configurations.

Another approach to workaround the issue is to only evolve logic function of the target application, not including routing. This route is followed by Tyrrell et al.: a custom-off-the-shelf hardware friendly evolutionary system was proposed [48] and a robot controller was implemented to verify the system. This approach is normally more efficient in terms of resource consumption. In addition, it can feature faster re-configuration. In this work, a Virtex FPGA will be targeted. In order to support safe intrinsic evolvability, only logic of the circuits will be evolved. The logic is built using evolvable molecule, which will be discussed in 8.1.1.

A real-world application, compression of image data with very high resolution, was considered in [49] and the compression method and hardware chip architecture were devised as well. They deployed FPGA to implement their EHW platform. The results suggested that when implemented in chip it can achieve a speed 2 magnitude faster than its software counterpart.

All of the projects about IEHW referenced above are of type semi-IEHW. However full-IEHW was increasingly attracting researchers.

Kajihara et al. investigated two chips in [50] and [51]: the first one was a gate-level evolvable chip which integrated all the necessary components of a full-IEHW, including evaluation of individuals, GA and control logic, and it was found that this chip could dramatically improve the evolution process; a DSP reconfiguration structure for neural network application was composed in the latter paper and it exhibited two orders of magnitude performance improvement than a Sun Ultra 2. Recently, full-IEHW platforms were designed and implemented for two industry applications [54] and [56] to improve performance so that they are more suitable to be employed in commercial products. An online adaptive and IEHW was realized to carry out the packet switching tasks in

network [54], while Yang and others proposed and implemented an IEHW platform to evolve novel image filter digital circuits employing CGP [56].

More recently, Rajan et al. conceived a dynamically reconfigurable circuit (DRC) based on FPGA to implement image filters [145]. The implementation in FPGA can react to the noise in the input image: if the noise increases, the FPGA will be dynamically reconfigured to deploy a more accurate (but slower) DRC filter. When the noise level drops down, a faster filter will be *swapped* back. They demonstrated that, with the FPGA implementation, 2 magnitude of speedup can be obtained compared to running it in software with a Pentium 4 2.8GHz processor.

Based on these researches, an IEHW platform will be investigated in Chapter 8 to obtain a better performance.

#### 2.5 Limitation of EHW

Although EHW alone is quite competitive to discover solutions for some applications, it does has several limitations, one of which is that evolution can not provide desirable integrated fault tolerance and adaptation, widely processed by multi-cellular living organism.

One way to tackle the constraint of EHW is to draw inspirations from biological principles. In this thesis, development principles will be discussed and considered in order to overcome the issue.

# 2.6 Summary

In this chapter, we gave an overview of the principles of evolutionary design and highlighted the key components in evolutionary design, the Evolutionary Algorithms. Afterwards, we discussed in further detail about a specific area of evolutionary design, evolvable hardware, which is the focus of this thesis. We presented the classification of EHW and reviewed some of the previous related projects in extrinsic evolvable hardware and intrinsic sub areas, which show the potentials of evolvable hardware as a design approach.

#### Chapter 2 Evolutionary Design of Electronic Systems

In this project, a special type of GP evolutionary algorithm will be used and we will deal with digital systems with extrinsic evolvable hardware first, and then implement an intrinsic platform to improve performance.

To deal with the limitations of EHW, developmental principles of biology will be considered. In the following chapter, the principle is reviewed and developmental electronic/mathematic systems which are the inspiration sources of this work.

# **Chapter 3**

# **Development Principles and Development**

# **Systems**

We overviewed the evolutionary design methodology and evolvable hardware principles in the previous chapter. Different types of EHW projects were also reviewed to demonstrate the characteristics of evolvable hardware. As development is the evolutionary selected approach to build complex systems, such as multi-cellular living creatures, developmental principles will be the sources of inspiration for this project.

The focus of this chapter is to present the basic principles of biological development and discuss some of the mathematical models proposed for development. Finally we highlight some existing development models specifically designed to be oriented towards electronic systems.

## 3.1 Biological Development Principles

Modern developmental biology<sup>5</sup> focuses on biological development<sup>6</sup>, cell growth and cell differentiation. Biological development studies the mechanisms that control the spatial distribution of different specialized types of cells and which lead to the forms of tissues, organs, organisms and the body anatomy.

Specifically, this sub section briefly reviews the principles of embryo development, which is the direct inspiration source of this research work.

## 3.1.1 Basic Concepts

Biology introduces a large number of glossaries, some of which have been borrowed by electronics to represent similar but fundamentally different

<sup>&</sup>lt;sup>5</sup> Developmental biology is a science branch in which the growth and development of organisms are studied.

<sup>&</sup>lt;sup>6</sup> Biological development is also known as morphogenesis.

principles. We discuss some of these glossaries and their corresponding meanings in computation and electronic systems.

#### 3.1.1.1 Chromosomes and Genes

Deoxyribonucleic Acid (DNA) is a type of acid found in nucleus of living cellular organism cells, which conveys genetic information that directs how to carry out the functions of the cell and the process of replication. The overall DNAs in an organism are normally organised in the form of chromosomes. DNA directs development of cells via the synthesis of proteins which perform the activities and replication of the cell.

The minimal heredity units encoded in the chromosomes are called genes. They determine the physics characteristics, development and behaviour of the organism and encode the information necessary for proteins synthesis.

In the evolvable hardware context, chromosome is borrowed from biology to represent the aggregate of heredity information. Chromosomes in EHW may take the form of strings of integers, trees or indexed graphs.

#### 3.1.1.2 Genotype and Phenotype

Before introducing genotype and phenotype, another definition is required to define them: alleles. In most living beings, one gene can be present in more than one viable chromosome. An allele refers to any one of them.

The aggregation of the alleles for a specific gene is termed the genotype for the gene. The physical outcome or appearance of the gene is called phenotype of the gene. In the perspective of a entire organism, rather than a particular gene, genotype can also be used to denote all the inheritable information, while phenotype in this context refers to the appearance and or performance of the individual.

Although genotype is the most influencing factor, the phenotype is not exclusively determined by genotype. Environmental factors also play an important role in the finalization of the phenotype from the genotype. On the other hand, a particular phenotype may result from a wide variety of slightly different genotypes. [18]

Normally, in EHW context, each gene only has one allele, so genotype is used to refer to the entire inheritable information (including all the genes). Phenotype in EHW also refers to the net outcome of the genotype in the form of final solutions.

#### 3.1.2 Biological Living Organism Cells

| Component |                   | Function                             |                                                 |  |  |  |  |  |

|-----------|-------------------|--------------------------------------|-------------------------------------------------|--|--|--|--|--|

| Nuclear   | DNA               | Carrier of hereditary information    |                                                 |  |  |  |  |  |

| region    | Enzymatic systems | •                                    | Duplicating the hereditary information          |  |  |  |  |  |

| Cytoplasm |                   | •                                    | Synthesizing proteins and most of the molecules |  |  |  |  |  |

|           |                   | •                                    | Generation of chemical energy                   |  |  |  |  |  |

|           |                   | Conduction of stimulus signals       |                                                 |  |  |  |  |  |

|           |                   | •                                    | Transport of materials                          |  |  |  |  |  |

| Membrane  |                   | •                                    | A continuous outer boundary                     |  |  |  |  |  |

|           |                   | Selection of water-soluble molecules |                                                 |  |  |  |  |  |

|           |                   | •                                    | Recognition and binding of molecules            |  |  |  |  |  |

Table 3-1 Biological Cell Components and their functions

Cells are the elementary structural and functional units of all living cellular organisms: the sub-structures of the cell are unable to retain the basic qualities of life, such as growing, reproducing or responding to outside stimuli in a coordinated, but potentially independent fashion. Thanks to the extremely organized molecular and biochemical systems, cells can store information in the form of heredity material DNA, utilizing it to synthesize cellular molecules and generate the necessary power to support all these functions from sources of chemical energy. In addition, cells are capable of motility and can tolerant environmental fluctuations by changing their internal biochemical systems. One of the most significant functions of cells is the ability to duplicate themselves by passing on their inherited information and their major biochemical and molecular systems to their offspring in the cellular reproduction process. [1]

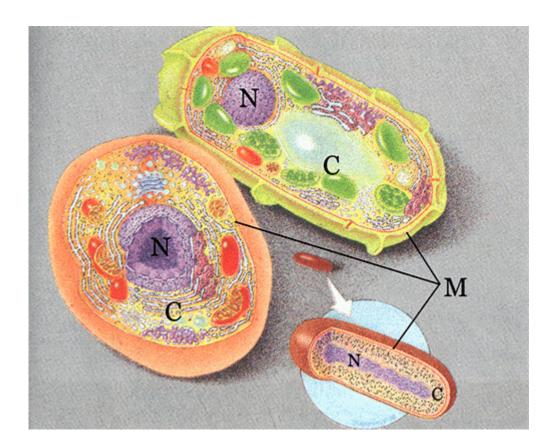

Figure 3-1 Overview Biological Cell Structure<sup>7</sup>

The nuclear region (N), the cytoplasm (C) and the membrane (M)

In spite of cells having an immense number of diversified forms in multicellular living organisms in terms of size, shape and function (see Figure 3-1), all cells have two common major internal regions divided by their nature of function (See Table 3-1): The first core part is *nuclear region* containing DNA molecules and enzymatic systems. The DNA molecules are the carriers of the hereditary information which directs cell growth and duplication in the cell. The enzymatic systems perform the task of duplicating the hereditary information for both cell reproduction and instructing the synthesis of various proteins. The other core region, the *cytoplasm*, synthesizes proteins and most of the other molecules necessary for the proper functioning of a living cell. This region also conducts other vital tasks, among the most significant of which are the generation of chemical energy usable by the cell, the conduction of stimuli from outside to interior, the transport of materials to and from the cell, and cell movement. [1]

<sup>&</sup>lt;sup>7</sup> The original picture was published in [1]

Another common feature of all cells is a continuous outer boundary, called *membrane*, that separates the cell contents from the exterior: membranes maintain cells as distinct environments and collections of matter. The most important task of membranes is to control what material can pass from one side to another and the amount of the particular material in a cell. [1]

#### 3.1.3 Stages of Development

The development of an embryo is determined by genes, which control where, when and how many proteins are synthesized [1]. Complex interactions between various proteins and between proteins and genes within cells and hence interactions between cells are set up by activities of genes. It is these interactions that control how the embryo develops. These interactions are normally referred to as Gene Regulatory Networks (GRN).

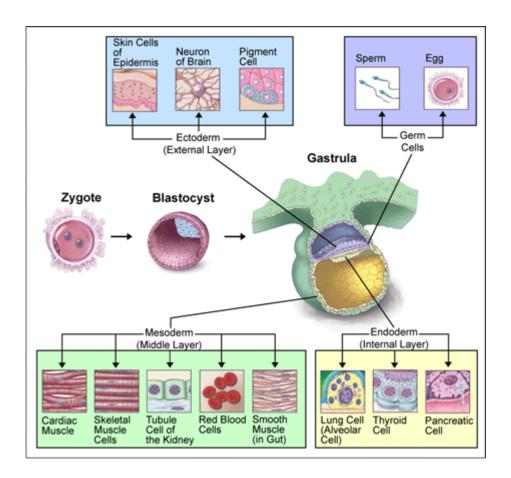

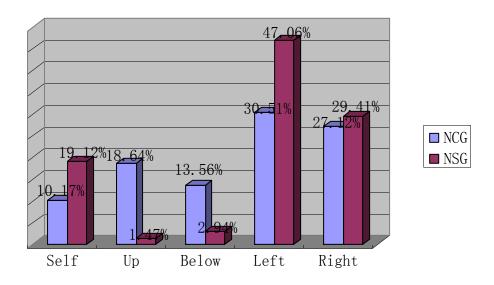

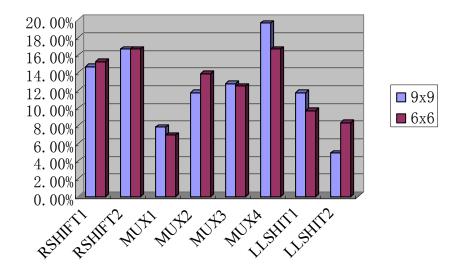

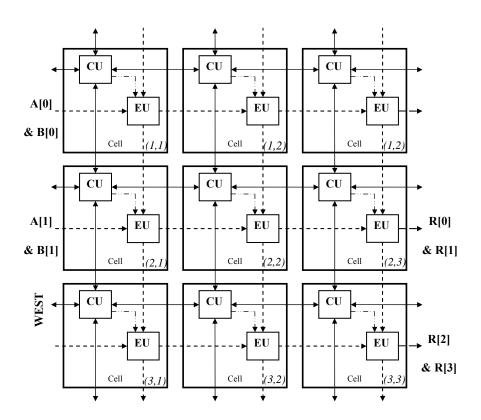

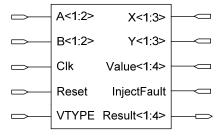

Embryo development involves five stages: cell division, the emergence of pattern, change in form, cell differentiation and growth. In the beginning, the zygote undertakes a rapid cell division<sup>8</sup>, called cleavage. Next, a spatial and temporal pattern of cell activities is organized within the embryo so that a well-ordered structure can develop, the process of which is called pattern formation. Then the form is changed to lay the fundamental for further development. Afterwards, cell differentiation (see Figure 3-2) is triggered in which cells become structurally and functionally different from each other, ending up as distinct cell types. Finally, they grow to increase their sizes in their determined location in order to divide into daughter cells..